Digital design is the foundation of modern technology, powering everything from smartphones and laptops to cutting-edge AI systems and autonomous vehicles. At its core, digital design revolves around creating hardware architectures capable of processing data efficiently. To bring these designs to life, engineers use Hardware Description Languages (HDLs)—specialized programming languages designed for modeling and simulating digital circuits. Among these HDLs, Verilog stands out as a cornerstone in the field of digital design.

Verilog is more than just a language; it’s a tool that bridges the gap between abstract ideas and tangible hardware implementations. Introduced in the mid-1980s, Verilog quickly became one of the most popular HDLs due to its simplicity, flexibility, and ability to describe complex digital systems concisely. Whether you’re working on basic combinational circuits or intricate system-on-chip (SoC) designs, Verilog provides the necessary syntax and functionality to capture your ideas effectively.

In the semiconductor and electronics industries, Verilog plays an indispensable role. Modern devices rely on integrated circuits (ICs), which require detailed designs for components like processors, memory units, and communication interfaces. Verilog helps engineers model, simulate, and verify these components before committing to physical fabrication. This ability to test and iterate in a virtual environment significantly reduces costs and development time, making Verilog essential for companies looking to stay competitive in a fast-paced industry.

Moreover, Verilog’s importance extends beyond professional applications. It serves as an entry point for students and hobbyists venturing into digital design. Its wide adoption in academia ensures that the next generation of engineers is well-equipped to handle real-world challenges. Open-source tools and resources further bolster its accessibility, enabling learners to experiment with digital circuits without expensive software licenses.

As technology evolves, so does the demand for skilled engineers proficient in Verilog. The language’s compatibility with industry-standard tools and its ability to support various abstraction levels—from gate-level descriptions to behavioral modeling—ensure its relevance in emerging fields like artificial intelligence, IoT, and quantum computing.

What is Verilog?

Verilog is a Hardware Description Language (HDL) used for modeling, simulating, and synthesizing digital circuits. It provides a structured way to describe hardware behavior and structure, enabling engineers to design complex systems efficiently. Unlike traditional programming languages, Verilog is specifically tailored for hardware design, making it indispensable in the field of digital design and electronics.

The origins of Verilog date back to the 1980s when it was developed by Gateway Design Automation. The language was designed to simplify the process of hardware design, providing engineers with a tool to describe circuits at various levels of abstraction, from high-level functional models to detailed gate-level implementations. Verilog’s intuitive syntax, inspired by programming languages like C, contributed to its rapid adoption within the industry.

In 1990, Gateway Design Automation was acquired by Cadence Design Systems, which played a pivotal role in Verilog’s proliferation. To promote widespread adoption and standardization, Verilog was eventually released into the public domain and standardized by the IEEE in 1995 as IEEE Standard 1364. Subsequent updates, such as SystemVerilog, have expanded Verilog’s capabilities, integrating advanced features to support modern design challenges.

As an HDL, Verilog allows designers to model both the structure and behavior of digital systems. At the structural level, it defines how components like gates, flip-flops, and multiplexers are interconnected. At the behavioral level, it describes how the system operates using constructs like always blocks, conditional statements, and loops. This versatility makes Verilog suitable for various stages of the design process, including simulation, verification, and synthesis.

Simulation is a critical aspect of digital design, and Verilog excels in this domain. By enabling engineers to simulate a design’s behavior before physical implementation, Verilog helps identify potential issues early, reducing development time and costs. Additionally, Verilog’s compatibility with popular simulation tools ensures seamless integration into existing workflows.

Beyond simulation, Verilog is widely used for synthesizing digital circuits. Synthesis translates Verilog descriptions into netlists, which can then be mapped to physical hardware like Field-Programmable Gate Arrays (FPGAs) or Application-Specific Integrated Circuits (ASICs). This capability underscores Verilog’s importance in transforming high-level ideas into functional hardware designs.

Key Features

Verilog is a versatile and powerful Hardware Description Language (HDL) that has become a cornerstone of digital circuit design. One of the key factors behind its widespread adoption is its conciseness and simplicity. Verilog’s syntax is designed to be easy to learn, making it accessible for engineers, students, and hobbyists alike. The language provides a straightforward way to describe hardware behavior, reducing the complexity of designing intricate digital circuits. This simplicity allows engineers to focus on the design itself rather than becoming bogged down by language complexity.

Another significant feature of Verilog is its support for multiple modeling styles, including structural, behavioral, and RTL (Register Transfer Level) modeling. Structural modeling is used to describe how hardware components are connected to one another. In this modeling style, engineers define the components (such as gates, flip-flops, and multiplexers) and the connections between them. Behavioral modeling, on the other hand, focuses on describing the behavior of the system without specifying its structural implementation. Engineers use high-level constructs, such as if-else statements or loops, to describe the desired behavior. RTL modeling is a critical feature of Verilog, as it allows designers to specify how data is transferred between registers and how operations are performed on that data at the register level. This versatility in modeling allows engineers to choose the most appropriate approach based on the design requirements, offering flexibility in capturing different aspects of a circuit.

Verilog is also highly compatible with both simulation and synthesis tools, two essential components of the digital design workflow. Simulation is used to verify the functionality of a design before it is physically implemented. Verilog’s compatibility with simulation tools, such as ModelSim or VCS, enables engineers to test their designs in a virtual environment. This helps identify potential issues early in the development process, reducing the time and cost of debugging hardware. Synthesis, on the other hand, is the process of converting a high-level Verilog description into a netlist—a set of gates and connections that can be physically implemented on an FPGA or ASIC. Verilog’s ability to work seamlessly with synthesis tools, such as Synopsys Design Compiler or Xilinx Vivado, ensures that designs can be efficiently mapped to actual hardware.

Another critical feature of Verilog is its standardization and interoperability with other tools. As an IEEE standard, Verilog ensures that designs created in the language can be easily shared and understood by different teams, tool vendors, and design environments. This standardization has led to Verilog’s widespread use across the industry, from small startups to large corporations. The language’s compatibility with a wide range of EDA (Electronic Design Automation) tools also ensures that engineers can integrate it with other design tools used in the industry, further cementing its role as a central language in digital design.

Why is Verilog Important?

Verilog has established itself as a dominant force in digital circuit design workflows due to its versatility, ease of use, and wide support from both academic and industrial communities. Its importance in modern hardware design cannot be overstated, as it has become an integral part of the digital design process, enabling the creation of complex systems with greater efficiency and accuracy.

One of the main reasons for Verilog’s dominance in digital circuit design is its deep integration into the design workflows of engineers. Verilog allows for the description of digital circuits at various levels of abstraction, from high-level behavioral models to detailed gate-level descriptions. This makes it suitable for all stages of the design process, including simulation, verification, and synthesis. Engineers can model a design, simulate its behavior, and then synthesize it into hardware using Verilog, all within a single workflow. This streamlining of the design process saves time and reduces the potential for errors, making Verilog a crucial tool in the development of modern digital systems.

Moreover, Verilog is widely taught in academic institutions around the world. As a fundamental tool in digital design education, Verilog provides students with the knowledge and skills they need to succeed in the field of hardware engineering. Learning Verilog exposes students to the principles of digital design and helps them understand how hardware systems are created, tested, and optimized. The language’s widespread use in academia ensures that the next generation of engineers is equipped with the skills necessary to work with the language in real-world applications. This widespread academic adoption has helped Verilog maintain its relevance in the rapidly evolving field of digital design.

In addition to its importance in education, Verilog also plays a critical role in the development of FPGAs (Field-Programmable Gate Arrays) and ASICs (Application-Specific Integrated Circuits). These two types of hardware are central to modern electronic systems, from consumer electronics to high-performance computing. Verilog is extensively used for designing both FPGAs and ASICs, providing engineers with the ability to describe hardware designs that can be mapped to these devices. The language’s compatibility with FPGA development tools like Xilinx Vivado or Altera Quartus, as well as ASIC tools like Synopsys Design Compiler, has made it the go-to language for many engineers working in these fields. With Verilog, engineers can design and verify circuits before implementing them on FPGAs or ASICs, enabling rapid prototyping and minimizing the risk of errors in the final hardware.

Verilog’s role in enabling rapid prototyping is another key factor in its importance. The ability to simulate and test a design virtually allows engineers to experiment with different configurations and functionality without the need for physical hardware. This significantly accelerates the prototyping process, allowing for faster iterations and improvements. Furthermore, this early testing reduces the cost and time associated with physical prototypes, making the development cycle more efficient. As hardware becomes more complex and integrated, rapid prototyping has become essential, and Verilog’s support for simulation and synthesis is a key enabler of this capability.

Finally, Verilog plays a significant role in reducing development costs. By providing engineers with a reliable and efficient way to model, simulate, and synthesize digital circuits, Verilog helps reduce the need for costly design revisions and physical testing. Early detection of design flaws in the simulation phase means that engineers can address issues before committing to hardware, saving both time and money. Additionally, Verilog’s integration with automated synthesis tools ensures that designs are optimized for performance and area, further reducing the cost of physical implementations.

In summary, Verilog is a critical tool in the world of digital design. Its ability to support structural, behavioral, and RTL modeling, combined with its compatibility with simulation and synthesis tools, has made it the language of choice for engineers working on complex digital systems. The language’s dominance in digital circuit design workflows, its widespread adoption in academia, and its support for FPGA and ASIC development ensure that Verilog will remain a key player in the field of hardware design for the foreseeable future. Moreover, its role in enabling rapid prototyping and reducing development costs makes it indispensable for companies looking to create cutting-edge hardware in an increasingly competitive industry.

Applications of Verilog

Verilog is a powerful and versatile Hardware Description Language (HDL) widely used in the digital design process. Its applications span various domains of electronics and semiconductor industries, ranging from basic digital logic design to complex system-on-chip (SoC) development. Let’s explore some of the key applications where Verilog plays an integral role.

Digital Logic Design and Verification

One of the primary uses of Verilog is in the design and verification of digital logic circuits. Engineers use Verilog to model the behavior and structure of circuits such as adders, multiplexers, flip-flops, and more. These building blocks are essential for designing larger systems like microprocessors and memory controllers. By describing the functionality and interconnections of logic gates and flip-flops, Verilog provides a clear, structured way to specify how a digital circuit should behave.

Verification is a critical part of digital design, and Verilog shines in this aspect. With the use of simulation tools like ModelSim and VCS, engineers can test their designs before committing them to hardware. They can simulate the digital logic, check for errors, and verify that the behavior aligns with the design specifications. The ability to verify circuits through simulation reduces costly mistakes during the physical implementation phase, ultimately leading to more reliable and efficient designs.

FPGA Programming and Development

Verilog is extensively used for FPGA (Field-Programmable Gate Array) programming and development. FPGAs are reconfigurable hardware devices that allow designers to implement custom logic circuits. They are used in various applications, from consumer electronics to aerospace systems, where flexibility and reusability are critical.

When designing FPGAs, Verilog serves as the language to describe the logic for the hardware’s configuration. Engineers use Verilog to specify the desired functionality of the FPGA, and synthesis tools like Xilinx Vivado or Intel Quartus then convert the Verilog code into configuration files that program the FPGA. One of the main advantages of using Verilog for FPGA design is that it allows engineers to quickly prototype and test custom logic without requiring the fabrication of new chips. This enables rapid development cycles and allows for easier experimentation and debugging.

Additionally, Verilog’s compatibility with simulation tools helps engineers thoroughly test their FPGA designs before programming the hardware, reducing the risk of design errors in the final product. With Verilog, designers can also take advantage of FPGA-specific features like parallelism and pipelining to optimize performance in high-speed or real-time applications.

ASIC Design Workflows

In ASIC (Application-Specific Integrated Circuit) design, Verilog plays a central role in modeling, simulating, and synthesizing custom chips. ASICs are designed for specific applications, such as mobile devices, networking equipment, or consumer electronics. The design process for ASICs is much more rigid than FPGAs, as ASICs are permanently fabricated with fixed logic, and mistakes in design can be very costly.

Verilog allows designers to describe ASIC components at various levels of abstraction, from high-level functional behavior to detailed gate-level implementations. Designers can simulate and verify their designs using tools like Synopsys Design Compiler, ensuring that the final chip performs as intended. Verilog also enables the synthesis of designs from a high-level description into a gate-level netlist that can be physically implemented on silicon.

As with FPGA development, the ability to simulate and test an ASIC design in Verilog before committing to physical fabrication is a significant advantage. It allows engineers to identify and address potential issues early in the design process, saving both time and money in the long run. Furthermore, Verilog’s compatibility with various EDA (Electronic Design Automation) tools makes it a standard language in ASIC design workflows, contributing to its popularity in the semiconductor industry.

Creation of Reusable Hardware Modules

Another important application of Verilog is in the creation of reusable hardware modules. In digital design, engineers often need to create modular components that can be reused across different projects. For instance, a universal adder, multiplier, or memory controller might be used in multiple designs, whether for FPGAs, ASICs, or custom SoCs. Verilog allows engineers to develop these modules by describing the hardware functionality and interconnection in a flexible, reusable format.

The modular nature of Verilog makes it an ideal language for designing components that can be easily shared and repurposed. With Verilog, engineers can define parameterized modules, enabling them to create hardware components that can be configured with different sizes, input-output configurations, or other parameters based on the specific needs of a project. This reduces development time and costs while promoting efficient design practices.

Comparison with Other HDLs

While Verilog is widely used in digital design, it is not the only Hardware Description Language available. Two other prominent HDLs are VHDL and SystemVerilog. Each of these languages has its strengths and weaknesses, and the choice of which one to use often depends on the specific requirements of a project.

Verilog vs. VHDL

VHDL (VHSIC Hardware Description Language) is another HDL that is widely used, particularly in the aerospace and defense sectors. While both Verilog and VHDL serve the same purpose—modeling and simulating digital systems—there are notable differences between the two.

One major difference is that Verilog has a syntax similar to the C programming language, which many engineers find easier to understand and use, especially for those familiar with programming. VHDL, on the other hand, is more verbose and has a syntax similar to Ada, which can make it more complex to learn for those without prior experience in software engineering.

Another key distinction is that Verilog is often considered more efficient for smaller, less complex designs, while VHDL is preferred for larger, more intricate designs that require a higher degree of abstraction. However, Verilog is typically favored for ASIC and FPGA development due to its simplicity and rapid simulation capabilities.

Verilog vs. SystemVerilog

SystemVerilog is an extension of Verilog that adds several features designed to improve its capabilities, especially in the areas of verification and design abstraction. SystemVerilog includes more advanced data types, object-oriented programming features, and assertions for formal verification.

While Verilog is often sufficient for many hardware designs, SystemVerilog is increasingly becoming the language of choice in industries that require higher levels of abstraction and advanced verification methods. Its enhanced features make it ideal for complex designs that involve verification and simulation. However, Verilog remains simpler and more intuitive for many engineers, particularly for smaller or less complex designs where the extra features of SystemVerilog may not be necessary.

Getting Started with Verilog

For those new to digital design or looking to start working with Verilog, the first step is to choose the right tools for writing and simulating Verilog code. Several EDA (Electronic Design Automation) tools support Verilog, making it easier for beginners to get started.

Tools for Writing and Simulating Verilog

Some of the most popular tools for writing and simulating Verilog code include:

- ModelSim: A widely used simulation tool for both Verilog and VHDL. It provides powerful debugging and visualization tools to help engineers simulate and verify their designs effectively.

- Xilinx Vivado: A comprehensive suite of tools for FPGA development, including Verilog-based synthesis, simulation, and debugging.

- Intel Quartus: Another popular FPGA development tool that supports Verilog and is used for designing and programming FPGAs.

- Icarus Verilog: An open-source Verilog compiler and simulator that is perfect for beginners who want to get hands-on experience without expensive software.

First Steps: Writing a Simple Verilog Module

To start working with Verilog, it’s essential to understand how to write a basic module. A simple Verilog module defines a small digital system, such as an adder or a flip-flop, and can be simulated to verify its functionality. Here’s an example of a simple Verilog module that describes a 2-input AND gate:

module and_gate (input a, input b, output y);

assign y = a & b;

endmoduleIn this example, the and_gate module has two inputs (a and b) and one output (y). The functionality is described using the assign statement, which connects the inputs with the output using the logical AND operator (&).

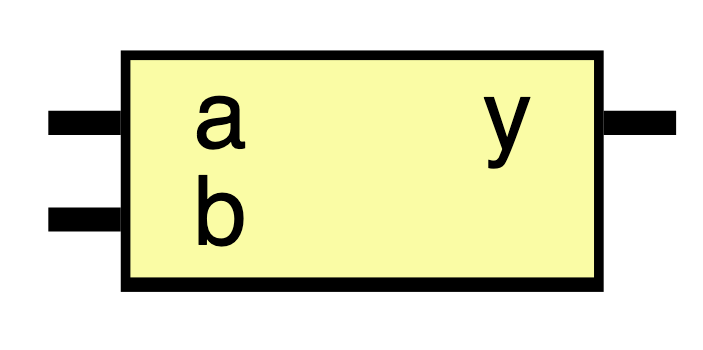

Here is the Block diagram of the code

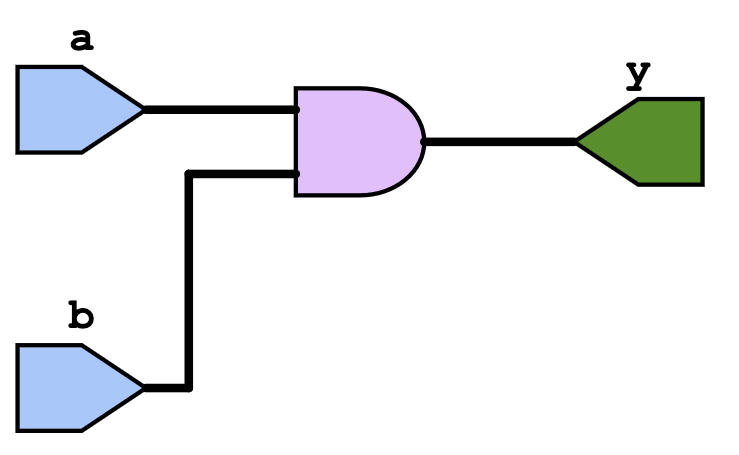

Here is the schematic

Resources for Beginners

For beginners looking to learn Verilog, there are several great resources available:

- Books:

- “Verilog HDL” by Samir Palnitkar is a well-regarded book that covers Verilog syntax, simulation, and design techniques.

- “Advanced Digital Design with the Verilog HDL” by Michael D. Ciletti is another excellent resource for learners who want to dive deeper into the language.

- Online Tutorials: Many websites and forums, such as Verilog Tutorial, provide step-by-step tutorials for beginners to get started with Verilog.

- Online Courses: Websites like Coursera, Udemy, and edX offer courses on digital design and Verilog, helping learners get hands-on experience with real-world examples and projects.

Getting started with Verilog may seem daunting at first, but with the right tools and resources, anyone can begin designing and simulating digital circuits efficiently. The versatility, simplicity, and wide support for Verilog make it an ideal language for both beginners and professionals alike.

Conclusion

In conclusion, Verilog stands as a cornerstone of digital design, playing an indispensable role in the creation, simulation, and synthesis of digital circuits. Whether used for FPGA development, ASIC design, or digital logic verification, Verilog has proven its versatility and efficiency. Its simplicity, widespread adoption, and compatibility with various design tools make it a preferred language for engineers across the electronics and semiconductor industries.

For those considering a career in digital electronics, mastering Verilog opens doors to a range of opportunities. As the demand for skilled engineers continues to grow in fields like AI, IoT, and embedded systems, proficiency in Verilog is an essential skill that can set you apart in the competitive tech industry.

If you’re just starting your journey into digital design, now is the perfect time to dive into Verilog. With numerous resources available, from books and tutorials to online courses, you can begin learning and practicing Verilog today. Embrace the challenge and explore how this powerful language can transform your ideas into tangible, functional hardware designs. Start your learning journey now, and unlock the potential of digital electronics with Verilog!

I’m an electrical engineer and chip designer pursuing a Master’s in Electrical Engineering at The University of Texas at Dallas. Passionate about digital design, I created Logic Flick to simplify complex concepts in Verilog, SystemVerilog, and UVM. Join me on this electrifying journey as we explore the world of digital electronics together!