In the world of digital design, Verilog stands as a foundational hardware description language (HDL) that enables engineers to model, simulate, and synthesize electronic circuits. Among the constructs that Verilog offers, the switch case in verilog plays a crucial role in creating structured and efficient conditional logic. Its utility extends to the design of finite state machines (FSMs), decoders, multiplexers, and more, making it a fundamental building block for digital systems.

The significance of the switch case in Verilog goes beyond its simplicity. By translating conditional logic directly into hardware, it ensures that designs are both efficient and optimized for real-world implementations. This article provides a detailed exploration of the switch case in Verilog, delving into its syntax, applications, practical examples, advanced techniques, and best practices.

The Role of Switch Case in Verilog HDL

Simplifying Decision-Making

Digital systems often require decision-making mechanisms to handle multiple conditions. While constructs like if-else can address simple cases, they become unwieldy when dealing with complex scenarios involving multiple branches. The switch case statement offers a cleaner, more organized approach, grouping related conditions and making the code easier to read and debug.

Mapping to Hardware

One of the unique aspects of Verilog is its direct mapping to hardware. A switch case statement in Verilog corresponds to multiplexers or other conditional hardware elements, ensuring that the code directly represents the underlying circuitry.

Scalability for Complex Designs

From small modules like decoders to large systems like FSMs, the switch case construct scales effortlessly. Designers can add new conditions without disrupting the structure of the existing code, making it an essential tool for modular and maintainable designs.

Syntax of Switch Case in Verilog

The syntax of the switch case statement in Verilog is straightforward yet versatile. Here’s the general structure:

always @(sensitivity_list) begin

case (expression)

condition1: begin

// Statements for condition1

end

condition2: begin

// Statements for condition2

end

default: begin

// Default case for unmatched conditions

end

endcase

endKey Components

- Sensitivity List: Defines when the

switch caseshould be evaluated, typically based on signal changes. - Expression: The variable being evaluated, often a signal or control input.

- Conditions: Each branch corresponds to a specific value of the expression.

- Default Case: Ensures graceful handling of unexpected inputs, preventing synthesis warnings and latches.

Examples of Switch Case in Verilog

Example 1: Basic 2-to-4 Decoder

A simple use case of the switch case statement is in a 2-to-4 decoder, which maps a 2-bit input to a 4-bit output.

module decoder_2to4 (

input clk, // Clock signal

input [1:0] control_signal, // Input control signal

output reg [3:0] out // Output of the decoder

);

// Always block sensitive to the rising edge of the clock

always @(posedge clk) begin

case (control_signal)

2'b00: out = 4'b0001;

2'b01: out = 4'b0010;

2'b10: out = 4'b0100;

2'b11: out = 4'b1000;

default: out = 4'b0000;

endcase

end

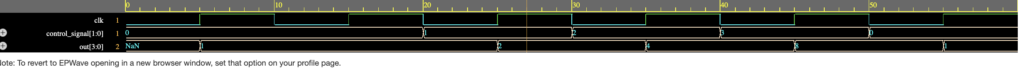

endmoduleOutput of the above code 2 to 4 decoder using switch case in verilog

Example 2: Multiplexer Implementation

The switch case is ideal for implementing multiplexers, which route one of several inputs to an output based on a selector.

module mux_4to1 (

input [3:0] data,

input [1:0] select,

output reg out

);

always @(select or data) begin

case (select)

2'b00: out = data[0];

2'b01: out = data[1];

2'b10: out = data[2];

2'b11: out = data[3];

default: out = 1'b0;

endcase

end

endmoduleExample 3: Finite State Machine (FSM)

Finite state machines (FSMs) often use switch case statements for clean and maintainable state transition logic. Here’s an example of a 3-state FSM:

module fsm_example (

input clk,

input reset,

input [1:0] command,

output reg [1:0] state

);

parameter IDLE = 2'b00, LOAD = 2'b01, EXECUTE = 2'b10;

always @(posedge clk or posedge reset) begin

if (reset)

state <= IDLE;

else begin

case (command)

2'b00: state <= IDLE;

2'b01: state <= LOAD;

2'b10: state <= EXECUTE;

default: state <= IDLE; // Safe fallback

endcase

end

end

endmoduleAdvanced Techniques and Best Practices to use Switch case in Verilog

Using Parameters for Readability

Replacing magic numbers with parameters improves code clarity and makes the design more maintainable.

parameter ADD = 2'b00, SUB = 2'b01, AND = 2'b10, OR = 2'b11;

always @(posedge clk) begin

case (opcode)

ADD: result = a + b;

SUB: result = a - b;

AND: result = a & b;

OR: result = a | b;

default: result = 4'b0000;

endcase

endCombining with Priority Encoding

For designs requiring prioritized conditions, use if-else in conjunction with switch case statements.

Simulation and Debugging Tips

- Use

$displaystatements in the default case to debug unexpected values during simulation. - Visualize

switch casebehavior with waveform tools to ensure correctness.

Applications in Real-World Designs

Arithmetic Logic Units (ALUs)

ALUs use switch case statements to select operations like addition, subtraction, and bitwise operations based on control signals.

State Machines in Embedded Systems

The simplicity of switch case enables efficient FSM design for control applications in embedded systems.

Decoders and Encoders

These circuits often rely on switch case for mapping inputs to outputs in communication protocols.

Common Mistakes and How to Avoid Them

- Missing Default Case: Always include a default case to prevent unintended behavior.

- Latch Inference: Ensure all conditions are covered to avoid unintentional latches during synthesis.

- Unoptimized Signal Widths: Match signal widths to the actual range of values to reduce hardware complexity.

Conclusion

The switch case in Verilog is a versatile and powerful construct, central to the design of modern digital systems. From FSMs to multiplexers, its applications are vast and impactful. By understanding its syntax, leveraging advanced techniques, and following best practices, designers can create robust and efficient hardware implementations.

Whether you’re a beginner exploring Verilog or an experienced designer, mastering the switch case statement is essential for efficient digital design. Explore more in-depth tutorials and resources at LogicFlick to deepen your understanding and enhance your skills.

I’m an electrical engineer and chip designer pursuing a Master’s in Electrical Engineering at The University of Texas at Dallas. Passionate about digital design, I created Logic Flick to simplify complex concepts in Verilog, SystemVerilog, and UVM. Join me on this electrifying journey as we explore the world of digital electronics together!